CONCURSO ITA 2025

EDITAL: 03/ITA/2025

CARGO: TECNOLOGISTA

## PERFIL: TL-12

### CADERNO DE QUESTÕES

1. Esta prova tem duração de **4 (quatro) horas**.

2. Você poderá usar **apenas** caneta esferográfica de corpo transparente com tinta preta, lápis ou lapiseira, borracha, régua transparente simples e compasso. **É proibido portar qualquer outro material escolar ou equipamento eletrônico**.

3. Esta prova é composta de **25 questões de múltipla escolha** (numeradas de 01 a 25) e de **3 questões dissertativas**.

4. Você recebeu este **caderno de questões, uma folha de leitura óptica e um caderno de respostas** que deverão ser devolvidos ao final do exame.

5. As questões de **múltipla escolha devem ser respondidas na folha de leitura óptica**. Assinale a opção correspondente à resposta de cada uma das questões, de **01 a 25**. Cada questão de múltipla escolha admite uma única resposta.

6. A folha de leitura óptica, deve ser preenchida usando caneta preta. Você deve preencher todo o campo disponível para a resposta, sem extrapolar os limites, conforme instruções na folha de leitura óptica.

7. Cuidado para não errar no preenchimento da folha de leitura óptica. Ela não será substituída.

8. Não haverá tempo suplementar para o preenchimento da folha de leitura óptica.

9. As **questões dissertativas devem ser respondidas no caderno de respostas**. Responda usando caneta preta, no campo destinado a cada questão.

10. **É obrigatória a devolução do caderno de questões, do caderno de respostas e da folha de leitura óptica**, sob pena de desclassificação do candidato.

11. **Aguarde o aviso para iniciar a prova. Ao terminá-la, avise o fiscal e aguarde-o no seu lugar.**

**Questão 1.** Considerando os princípios de operação das Máquinas de Estados Finitos (FSMs) em circuitos digitais, assinale a única alternativa CORRETA:

**A ( )** Em uma codificação binária mínima, o número de flip-flops necessários para representar uma FSM com  $N$  estados é sempre igual a  $\lceil \log_2 N \rceil$ , independentemente do número de transições entre estados.

**B ( )** Em uma máquina de Moore, as saídas podem mudar imediatamente após uma alteração nas entradas, desde que o próximo estado seja atualizado combinacionalmente.

**C ( )** FSMs do tipo Mealy apresentam atrasos maiores na saída que FSMs Moore, pois dependem apenas do estado armazenado nos flip-flops.

**D ( )** Uma FSM síncrona é aquela cujas transições de estado ocorrem apenas em resposta a mudanças assíncronas de entrada, não envolvendo sinais de clock.

**E ( )** O uso de codificação one-hot reduz o número de flip-flops necessários, porém aumenta a complexidade da lógica combinacional de próxima transição.

**Questão 2.** No fluxo de projeto físico de circuitos integrados digitais, diversas etapas garantem que o layout produzido seja funcional e fabricável. Sobre essas etapas, assinale a única alternativa CORRETA:

**A ( )** A etapa de *Placement* consiste em gerar o roteamento detalhado das interconexões metálicas do circuito, definindo largura, espaçamento e vias para cada trilha.

**B ( )** A verificação *ERC* (Electrical Rule Check) é utilizada para verificar regras geométricas de fabricação, como espaçamento mínimo e largura mínima de metal.

**C ( )** A análise de *IR Drop* verifica quedas de tensão nas linhas de alimentação, garantindo que todos os blocos recebam VDD e GND dentro de margens aceitáveis.

**D ( )** O *Clock Tree Synthesis (CTS)* é a etapa final do projeto físico, e consiste em comparar o layout extraído com o esquemático original para verificar conectividade.

**E ( )** O *Routing Global* garante que todas as conexões elétricas sejam realizadas com precisão geométrica, determinando exatamente o percurso final de cada fio metálico.

**Questão 3.** Considere o código VHDL abaixo, que pretende implementar uma porta lógica OR com duas entradas:

```

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY porta_or IS

PORT (

a : IN STD_LOGIC;

b : IN STD_LOGIC;

y : OUT STD_LOGIC

);

END porta_or;

ARCHITECTURE rtl OF porta_or IS

BEGIN

y = a OR b;

END rtl;

```

O código acima não compila devido a um erro de sintaxe na linha de atribuição. Qual correção deve ser aplicada para que o código funcione corretamente?

- A ( )** O operador "=" deve ser trocado por "==" para comparação lógica.

- B ( )** O operador "=" deve ser trocado por "<=" para realizar atribuição concorrente.

- C ( )** A instrução deve ser movida obrigatoriamente para dentro de um PROCESS.

- D ( )** O tipo das portas deve ser alterado para BIT.

- E ( )** O nome da arquitetura deve ser removido.

**Questão 4.** Um circuito de buffer composto por uma cascata de inversores CMOS com aumento da largura do canal progressiva (*tapered buffer*) contendo 5 estágios foi projetado para permitir o acionamento de uma capacidade de carga igual a 1024 vezes a capacidade de entrada de um inversor unitário. O valor do fator de aumento progressivo da largura de canal aplicado a cada estágio empregado neste buffer deve ser igual a:

- A ( )** 2,5

- B ( )** 3,0

- C ( )** 3,5

- D ( )** 4,0

- E ( )** 4,5

**Questão 5.** Considere as seguintes afirmações sobre a arquitetura RISC-V:

- I. A especificação RISC-V define instruções de 32, 16, 48 e 64 bits, permitindo extensões variáveis de comprimento além das instruções compactadas.

- II. A extensão "A" adiciona operações atômicas como LR/SC, fundamentais para sincronização em sistemas multiprocessados.

III. A extensão “F” adiciona suporte a operações com ponto flutuante em precisão simples, enquanto a extensão “D” adiciona ponto flutuante em precisão dupla.

IV. Toda implementação RISC-V que suporte operações de ponto flutuante precisa obrigatoriamente implementar também a extensão vetorial (V).

V. O modo de execução Machine (M-mode) é o único modo obrigatório na especificação RISC-V, podendo as implementações omitirem os modos Supervisor (S-mode) e User (U-mode).

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I, II e III.    B ( ) II, III e V.    C ( ) I, IV e V.    D ( ) I, II, III e V.    E ( ) II, IV e V.**

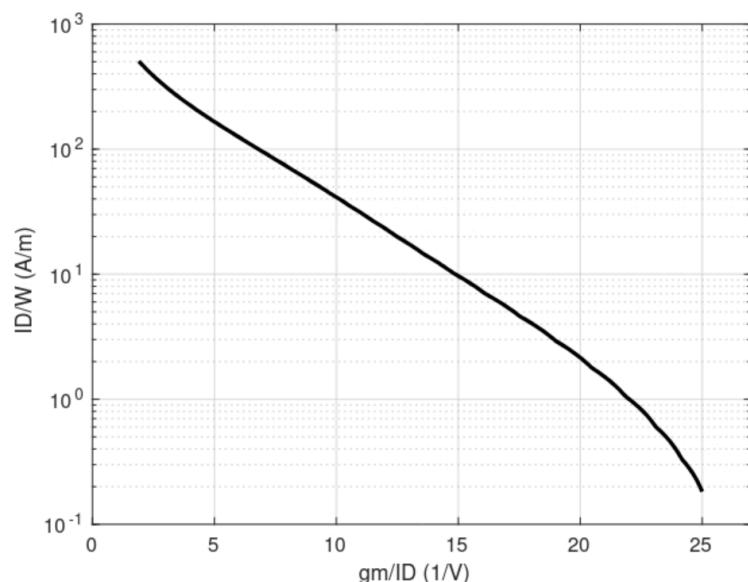

**Questão 6.** Considere a curva de densidade de corrente ( $ID/W$ ) em relação a  $gm/ID$  de um transistor NMOS para o valor de comprimento do canal ( $L$ ) de 180 nm.

Sabendo que um transistor NMOS que possui  $L=180$  nm e largura do canal ( $W$ ) de  $2\text{ }\mu\text{m}$  e foi polarizado de forma a possuir relação de transcondutância de gate ( $gm$ ) por corrente de dreno ( $ID$ ) igual a  $15\text{ V}^{-1}$ , qual é o nível aproximado de transcondutância de gate ( $gm$ ) que o transistor possui?

**A ( )  $50\text{ }\mu\text{S}$     B ( )  $100\text{ }\mu\text{S}$     C ( )  $200\text{ }\mu\text{S}$     D ( )  $300\text{ }\mu\text{S}$     E ( )  $500\text{ }\mu\text{S}$**

**Questão 7.** Considere as seguintes afirmações sobre a implementação de circuitos lógicos combinacionais em tecnologia CMOS:

**I.** Portas lógicas CMOS estáticas apresentam consumo praticamente nulo de potência quando não há comutação do nível lógico de saída.

**II.** A utilização de lógica de transmissão (Transmission Gate Logic) pode reduzir o número de níveis lógicos em comparação com CMOS estático, gerando maior atraso.

**III.** Chaves implementadas somente com transistores NMOS apresentam degradação ao conduzir nível lógico alto, devido ao efeito da tensão de limiar.

**IV.** Aumentar o fan-out de uma porta lógica reduz a capacidade de carga, o que tende a aumentar o atraso de propagação da porta.

**V.** Portas dinâmicas exigem mecanismos de retenção de carga, e podem perder seu valor lógico se permanecerem por tempo prolongado sem serem reavaliadas.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I, III e V    B ( ) II, III e V    C ( ) I, II e III    D ( ) I, IV e V    E ( ) III, IV e V**

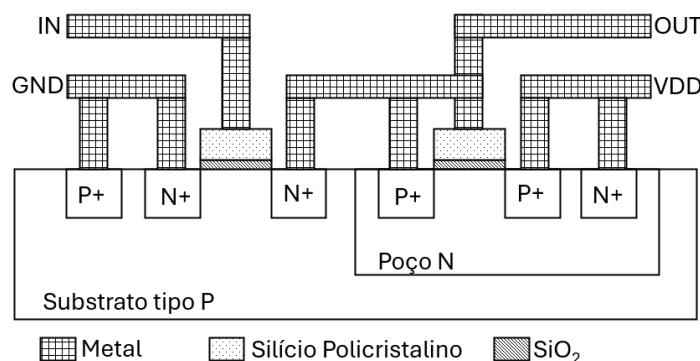

**Questão 8.** Considere que a imagem abaixo ilustra a vista em corte de um circuito implementado em tecnologia CMOS planar e que o circuito seja conectado à fonte de alimentação pelos terminais “VDD” e “GND”, tenha a sua entrada conectada ao terminal “IN” e saída ao terminal “OUT”.

Assinale a alternativa que contém uma afirmação VERDADEIRA:

**A ( ) A imagem representa uma porta lógica inversora CMOS.**

**B ( ) A imagem representa um amplificador fonte comum com carga ativa composta por um transistor PMOS operando como fonte de corrente.**

**C ( ) A imagem representa um amplificador fonte comum com carga ativa composta por um transistor PMOS operando em configuração de diodo.**

**D ( ) A imagem representa um amplificador fonte comum com carga ativa composta por um transistor NMOS operando como fonte de corrente.**

**E ( ) A imagem representa um amplificador CMOS do tipo push-pull.**

**Questão 9.** Considere as seguintes afirmações sobre o silício (Si) e semicondutores III-V (por exemplo, GaAs, InP):

- I.** O silício possui banda proibida indireta, o que o torna pouco eficiente como emissor de luz, embora seja amplamente utilizado em fotônica integrada (por exemplo, em plataformas SOI) para guias de onda e moduladores.

- II.** O arseneto de gálio (GaAs) apresenta mobilidade eletrônica típica maior que a do silício, o que favorece aplicações em alta frequência e micro-ondas.

- III.** O fosfeto de índio (InP) é o substrato de escolha para lasers e detectores operando em 1,3–1,55  $\mu\text{m}$  (telecomunicações) devido a seu bandgap e propriedades ópticas.

- IV.** Semicondutores III-V não podem ser combinados epitaxialmente em heteroestruturas devido a incompatibilidades de rede, o que limita sua utilização em dispositivos optoeletrônicos.

- V.** Heteroestruturas III-V (por exemplo, InGaAs/InP) permitem ajustar bandgaps e confinamento por engenharia de composição, sendo vantajosas para lasers, moduladores e células solares de alto rendimento.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I e IV.**   **B ( ) II, III e V.**   **C ( ) I, II e V.**   **D ( ) III e IV.**   **E ( ) I, II, III e V.**

**Questão 10.** Considere as seguintes afirmações sobre bibliotecas de células padrão (standard cells) e práticas de projeto físico para circuitos digitais CMOS:

- I.** As células padrão normalmente têm altura fixa (*row height*) para permitir colocação em fileiras contínuas, embora suas larguras possam variar conforme a complexidade funcional.

- II.** A densidade de *tracks* (número de trilhas de metal por célula) influencia tanto a facilidade de roteamento quanto a performance elétrica da biblioteca.

- III.** Para economizar área, é comum compartilhar poços (wells) e difusões entre células adjacentes, o que exige cuidado com a estratégia de tie-high/tie-low para evitar polarização inadequada do substrato.

- IV.** A etapa de caracterização de uma célula padrão não precisa considerar variações de processo, temperatura e tensão (PVT), pois essas variações serão tratadas apenas no nível do chip completo.

Das afirmações acima, são CORRETAS apenas:

**A ( ) I e II.**   **B ( ) II e III.**   **C ( ) I e IV.**   **D ( ) III e IV.**   **E ( ) I, II e III.**

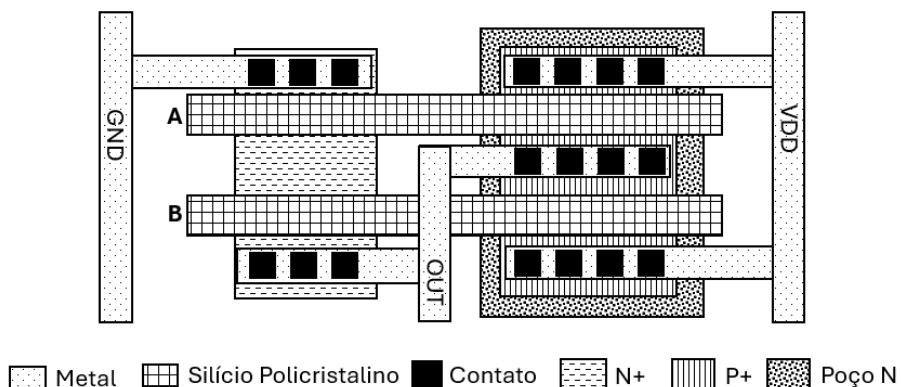

**Questão 11.** Considere o layout de uma porta lógica apresentado abaixo:

Assinale a alternativa que contém uma afirmação VERDADEIRA:

- A ( )** O layout representa uma porta lógica OR de duas entradas.

- B ( )** O layout representa uma porta lógica AND de duas entradas.

- C ( )** O layout representa uma porta lógica NOR de duas entradas.

- D ( )** O layout representa uma porta lógica NAND de duas entradas.

- E ( )** O layout representa uma porta lógica NOT de duas entradas.

**Questão 12.** Considere as seguintes afirmações sobre o consumo de energia em um inverter CMOS:

- I.** A energia consumida quando o inverter comuta entre níveis lógicos depende apenas da capacidade de carga e da tensão de alimentação, não sendo influenciada pela frequência de operação.

- II.** A potência dinâmica total dissipada por um inverter aumenta com a frequência de comutação do sinal de entrada.

- III.** O componente de perda devido ao curto-círcuito entre os transistores aumenta se os tempos de transição da entrada (rise/fall) forem mais lentos, porque ambos os transistores permanecem conduzindo simultaneamente por mais tempo.

- IV.** A potência estática originada por correntes de fuga tende a reduzir em tecnologias com dimensões de canal menores, mantendo-se a mesma tensão de alimentação.

Das afirmações acima, estão CORRETAS apenas:

- A ( ) I e II.**

- B ( ) II e III.**

- C ( ) I, III e IV.**

- D ( ) II, III e IV.**

- E ( ) I, II e III.**

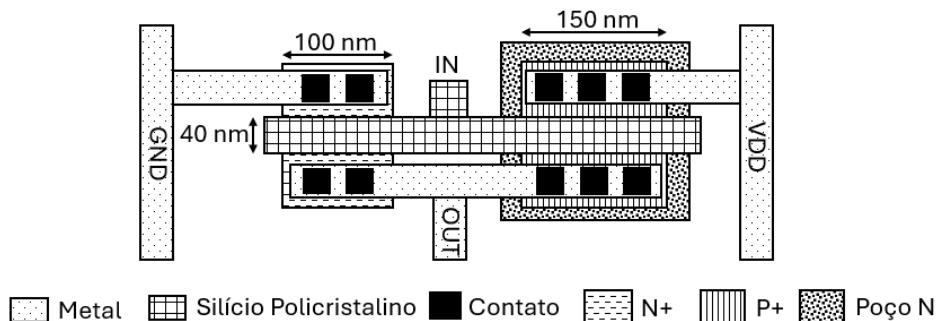

**Questão 13.** Considere o layout mostrado abaixo para analisar as afirmações:

- I.** A largura de canal do transistor PMOS é 3 vezes maior que a largura de canal do transistor NMOS.

- II.** Provavelmente o processo utilizado para fabricação trata-se de um nó tecnológico igual ou inferior a 40 nm.

- III.** O transistor PMOS possui comprimento de canal de 150 nm, enquanto que o transistor NMOS possui comprimento de canal de 100 nm.

- IV.** A polarização do substrato P e do poço N é realizada diretamente pelas linhas de alimentação de GND e VDD, sem utilização de células específicas para polarização.

- V.** Ambos os transistores NMOS e PMOS possuem comprimento de canal igual a 40 nm.

Das afirmações acima, são FALSAS apenas:

**A ( ) I, II e III.    B ( ) I, III e IV.    C ( ) II, III e IV.    D ( ) II, IV e V.    E ( ) III, IV e V.**

**Questão 14.** Considere as seguintes afirmações sobre a arquitetura interna e o funcionamento dos FPGAs (Field Programmable Gate Arrays):

- I.** As LUTs presentes nos blocos lógicos podem implementar funções combinacionais arbitrárias até um número máximo de entradas definido pela arquitetura.

- II.** Flip-flops disponíveis nas *logic cells* podem ser utilizados em qualquer tipo de lógica sequencial, como contadores, máquinas de estado e registradores.

- III.** O roteamento em um FPGA utiliza uma vasta rede de interconexões programáveis, cujo atraso pode variar dependendo do número de *switches* utilizados no caminho e da distância entre blocos lógicos.

- IV.** Em FPGAs baseados em tecnologia antifuse, a configuração é volátil e precisa ser regravada a cada inicialização do dispositivo.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I e III.    B ( ) II e IV.    C ( ) II e IV.    D ( ) I, III e IV.    E ( ) II, III e IV.**

**Questão 15.** Analise as seguintes afirmações sobre diferentes tipos de circuitos integrados e suas aplicações:

- I.** Microcontroladores (MCUs) normalmente não possuem periféricos integrados, como temporizadores, conversores A/D e interfaces de comunicação, sendo projetados para tarefas de controle em tempo real com baixo consumo de energia.

- II.** FPGAs são dispositivos reconfiguráveis após a fabricação, permitindo que a lógica interna seja modificada quantas vezes forem necessárias, inclusive durante a operação, em algumas arquiteturas.

- III.** ASICs tendem a apresentar menor consumo de energia e maior desempenho para uma aplicação específica, porém possuem elevado custo de desenvolvimento inicial devido ao processo de fabricação customizado.

- IV.** SoCs podem integrar múltiplos núcleos de CPU, aceleradores gráficos, blocos DSP, controladores de comunicação e até mesmo módulos de RF em um único chip, dependendo da aplicação alvo.

- V.** MCUs e ASICs compartilham a mesma característica fundamental de reconfiguração lógica via fusíveis, assim como os FPGAs.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I, II e III    B ( ) I, III e IV    C ( ) II, III e IV    D ( ) I, II e V    E ( ) III, IV e V**

**Questão 16.** No contexto de Teste e Validação de Circuitos Integrados (CIs), diversas metodologias de DFT (Design for Testability) e padrões industriais são utilizados para melhorar a cobertura de falhas e permitir diagnósticos eficientes. Cada alternativa abaixo descreve uma técnica relacionada ao teste de hardware.

Assinale a alternativa que contém uma afirmação FALSA:

**A ( )** Em arquiteturas com Scan Compression, os dados de teste são comprimidos antes de serem enviados ao chip, reduzindo significativamente o tempo de aplicação dos vetores sem comprometer a cobertura de falhas.

**B ( )** O BIST de memória (MBIST) utiliza algoritmos padronizados, como March C e March Y, para detectar falhas específicas de RAMs, incluindo falhas de transição, de retenção e de acoplamento entre células adjacentes.

**C ( )** A técnica de Boundary Scan permite testar interconexões entre chips montados em uma placa de circuito impresso, mesmo quando as trilhas não são acessíveis fisicamente por pontas de prova externas.

**D ( )** O software ATPG pode gerar vetores para modelos de falha estruturais, mas não pode ser utilizado para testes de transição ou falhas de atraso, pois esses modelos exigem verificação manual em nível funcional.

**E ( )** Em testes de at-speed, o circuito é exercitado em sua frequência real de operação, permitindo detectar falhas sensíveis ao tempo que não aparecem em testes com frequência reduzida.

**Questão 17.** Considere as seguintes afirmações relacionadas às etapas típicas de microfabricação em tecnologias CMOS:

**I.** A etapa de planarização por CMP (Chemical Mechanical Polishing) é utilizada para nivelar a superfície do wafer após deposições e gravações, garantindo uniformidade para as camadas subsequentes.

**II.** A deposição por evaporação térmica é o método preferido para formar dielétricos de porta (gate oxide) em tecnologias CMOS modernas.

**III.** A difusão térmica é um processo alternativo à implantação iônica para introduzir dopantes no silício, porém tem menor controle de profundidade e é menos usada em tecnologias avançadas.

**IV.** Na fotolitografia, a técnica de *deep UV* (DUV) permite padrões mais finos que a fotolitografia convencional, devido ao uso de comprimentos de onda menores.

**V.** A deposição ALD (Atomic Layer Deposition) é usada para criar camadas extremamente finas e uniformes, mas não pode ser empregada para materiais dielétricos, apenas para metais.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I e III    B ( ) II, III e IV    C ( ) I, III e IV    D ( ) II, IV e V    E ( ) III, IV e V**

**Questão 18.** Considere o esquemático do circuito lógico mostrado abaixo:

É correto afirmar que o circuito possui a função de:

- A ( )** Um circuito latch sensível à borda de subida do sinal de relógio.

**B ( )** Um circuito latch sensível ao nível baixo do sinal de relógio.

**C ( )** Um registrador lógico sensível ao nível alto do sinal de relógio.

**D ( )** Um registrador lógico sensível à borda de descida do sinal de relógio.

**E ( )** Um registrador lógico sensível à borda de subida do sinal de relógio.

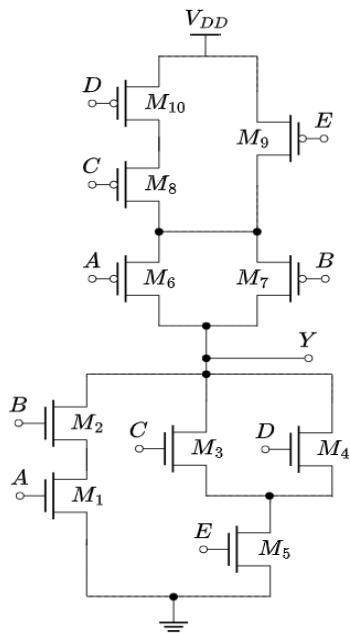

**Questão 19.** Dado o esquemático da porta lógica CMOS complexa seguinte:

A função lógica implementada por esta porta é:

- D** ( )  $Y = \overline{(A+B) \cdot [(C \cdot D) + E]}$  **E** ( )  $Y = [(A+B) \cdot C] + (D \cdot E)$

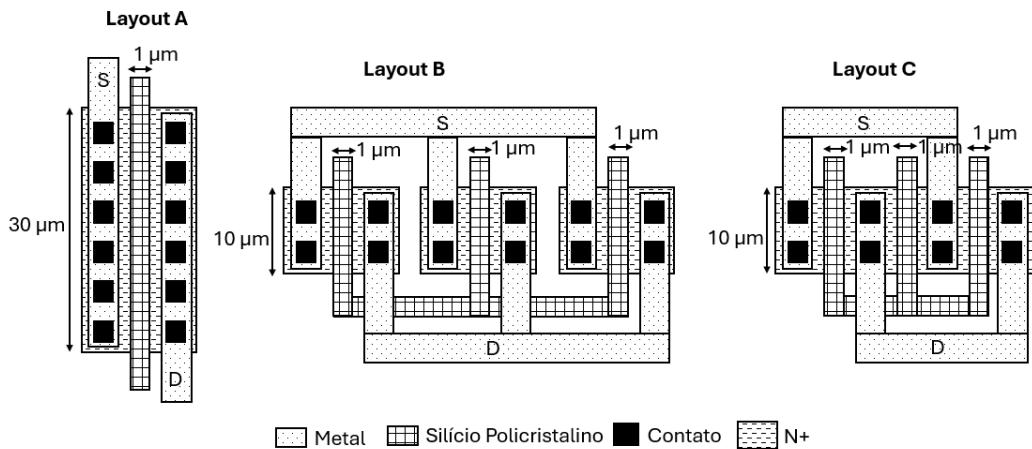

**Questão 20.** Considere os layouts A, B e C de um transistor NMOS mostrados abaixo:

- I. Os Layouts A, B e C representam transistores com largura e comprimento de canal equivalentes.

- II. O Layout A representa um transistor cuja largura de canal é 3 vezes maior que a largura de canal equivalente dos Layouts B e C.

**III.** O Layout A apresenta os mesmos valores de capacitância de Dreno (D) e Fonte (S) que o transistor do Layout B

**IV.** O Layout C apresenta os menores valores de capacitância de Dreno (D) e Fonte (S) em comparação aos layouts A e B.

**V.** A diferença no comprimento da região de difusão dos transistores não afeta o comportamento elétrico dos dispositivos.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I, II e III    B ( ) I, III e IV    C ( ) I, IV e V    D ( ) II, III e V    E ( ) III, IV e V**

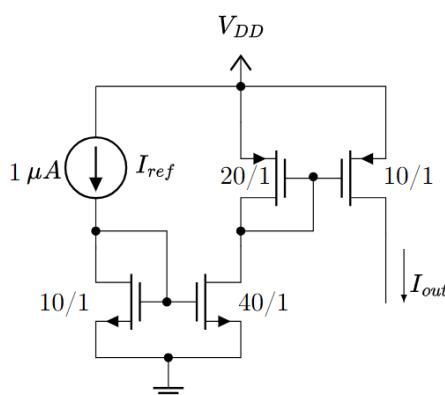

**Questão 21.** Considere que o circuito de polarização com espelhos de corrente apresentado abaixo esteja operando em saturação e o erro de espelhamento devido à diferença de tensão entre dreno e fonte seja desprezível.

Assinale a alternativa que apresente o valor CORRETO da corrente espelhada na saída ( $I_{out}$ ).

**A ( ) 1 μA    B ( ) 2 μA    C ( ) 4 μA    D ( ) 10 μA    E ( ) 20 μA**

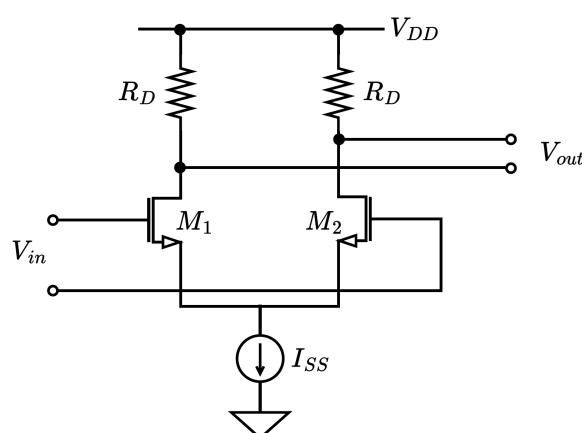

**Questão 22.** Dado o par diferencial apresentado na Figura abaixo, verifique as seguintes afirmações:

- I.** A fonte de corrente  $I_{SS}$  é responsável pela rejeição de modo-comum do amplificador.

- II.** Para obter um amplificador diferencial com saída em terminação simples, basta ignorar uma das saídas, não havendo necessidade de nenhuma modificação no circuito.

- III.** Para o correto funcionamento em malha fechada este amplificador necessita de um circuito de realimentação de modo-comum.

- IV.** O ganho de tensão poderia ser superior se os resistores fossem substituídos por transistores operando como fonte de corrente.

- V.** O circuito é imune a ruídos, uma vez que tanto o sinal de entrada quanto o sinal de saída são diferenciais.

Das afirmações acima, estão CORRETAS apenas:

- A** ( ) I, II e III    **B** ( ) I, III e IV    **C** ( ) I, IV e V    **D** ( ) II, III e V    **E** ( ) III, IV e V

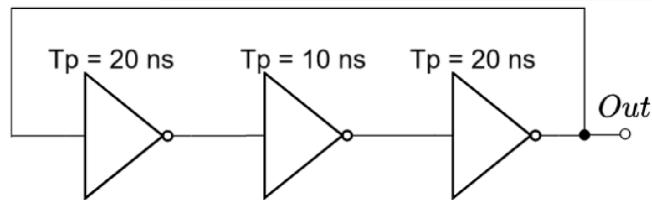

**Questão 23.** Considerando o circuito oscilador em anel mostrado na figura abaixo:

A frequência de oscilação obtida com este oscilador é:

- A** ( ) 20 MHz    **B** ( ) 15 MHz.    **C** ( ) 10 MHz.    **D** ( ) 7,5 MHz.    **E** ( ) 5 MHz.

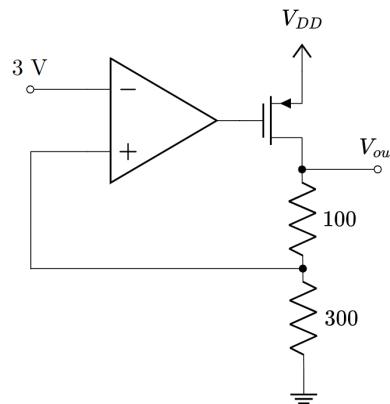

**Questão 24.** Considerando o circuito abaixo com amplificador operacional ideal e que o nível  $V_{DD}$  seja suficiente para polarizar o circuito:

O valor correto da tensão de saída ( $V_{out}$ ) é:

- A** ( ) 1,0 V    **B** ( ) 1,5 V    **C** ( ) 2,0 V    **D** ( ) 3,0 V    **E** ( ) 4,0 V

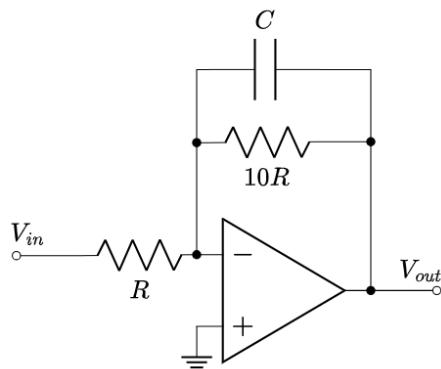

**Questão 25.** Dado o circuito mostrado abaixo, analise as seguintes afirmações:

- I.** O circuito implementa um filtro passa-alta com ganho na faixa de passagem equivalente a 10 dB.

- II.** O circuito implementa um filtro passa-baixa com ganho na faixa de passagem equivalente a 20 dB.

- III.** A frequência angular de corte do filtro equivale ao valor dado por  $1/(10.R.C)$ .

- IV.** O amplificador operacional deve possuir produto ganho-largura ao menos igual à frequência de corte do filtro.

- V.** O circuito realimentado é estável, independente do nível de margem de fase do amplificador operacional.

Das afirmações acima, estão CORRETAS apenas:

**A ( ) I e III    B ( ) II e III    C ( ) II e IV    D ( ) III e V    E ( ) IV e V**

**Questão Dissertativa 01.** Considerando que um projetista de circuito integrado analógico deseje projetar um amplificador operacional com elevado ganho de tensão, demonstre de forma clara quais são as vantagens e desvantagens entre a utilização de um amplificador diferencial de dois estágios com compensação Miller e um amplificador do tipo Cascode (Telescópico).

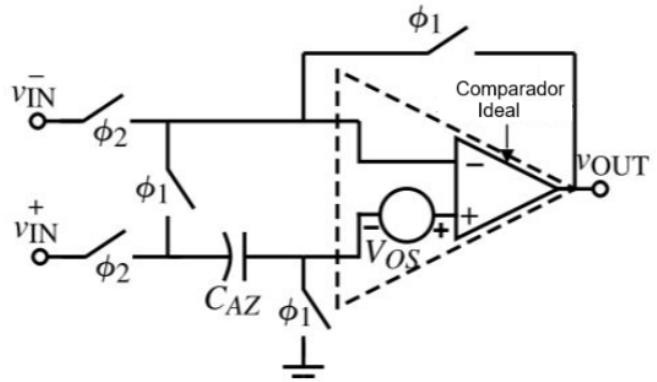

**Questão Dissertativa 02.** Sabendo que circuitos comparadores com baixo offset são necessários para a implementação de conversores de dados de alta resolução, detalhe o funcionamento, vantagens e desvantagens do comparador com cancelamento de offset apresentado abaixo:

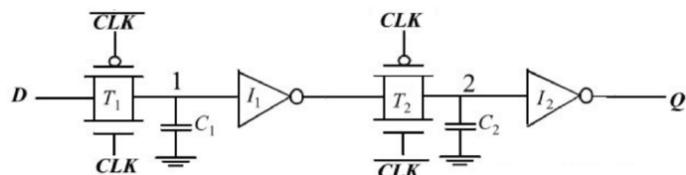

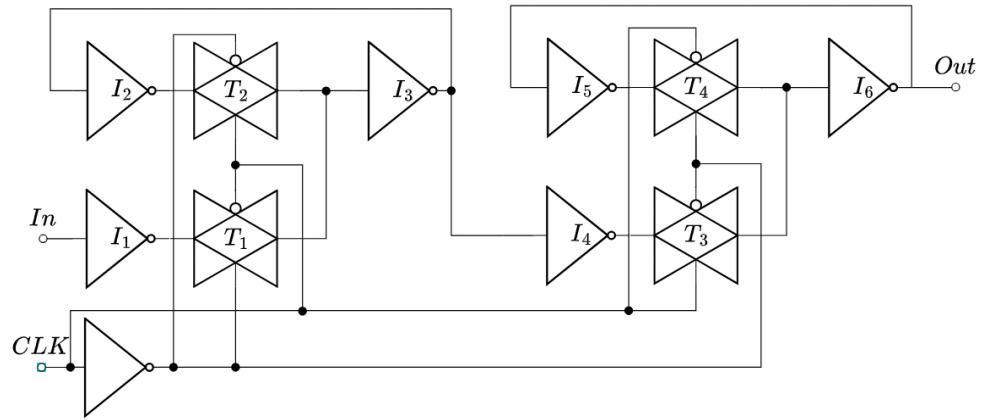

**Questão Dissertativa 03.** Detalhe o funcionamento do circuito abaixo e explique quais são os requisitos de tempos de *setup* e *hold* para o sinal de entrada em relação ao sinal de clock, considerando os atrasos presentes no circuito.

## RASCUNHO

---

## RASCUNHO

---

## RASCUNHO

---

## RASCUNHO

---